A Place to learn VHDL & Verilog HDL comparitively ...

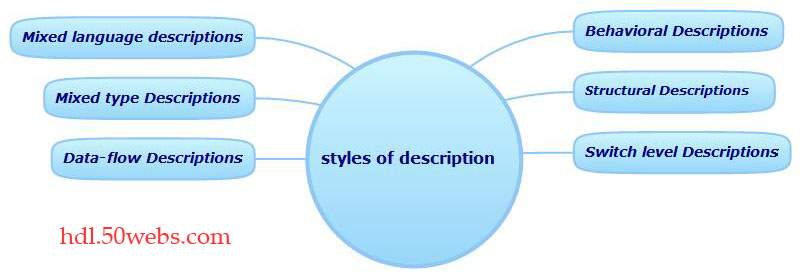

Chapter 1. styles of description

Styles of descriptions:

There are different styles of writing the descriptions both in VHDL and Verilog. These styles are broadly classified into 7 types as shown below. These styles are common to VHDL and Verilog HDL.

1. Behavioral description:

A behavioral description is based on the manner in which outputs behave with the inputs. In VHDL the architecture includes the keyword �process�. In Verilog �always� or �initial� is used.

To view code enlarged click here

To download code click here

2.Structural description:

In this description the entire system is modeled as components or gates. The description is identified by the presence of the key word �component� in architecture in VHDL. In Verilog it is identified by gates construct eg and, or.

To view code enlarged click here

To download code click here

3.Switch description:

The system is described into switches or transistors. Verilog uses keywords to describe the system. VHDL does not have built in switch level primitives but we can attach packages which contain them.

To view code enlarged click here

To download code click here

4.Data flow description:

Data flow description shows how the signals flow from the inputs to the output. The data flow statements are concurrent. The description usually has Boolean expression of its outputs.

To view code enlarged click here

To download code click here

5.Mixed type description:

Mixed type usually has more than one style of the descriptions in them. They are used in large sized programs.

6.Mixed language description:

Mixed language description is a new tool in which the user can write module in Verilog and entity from VHDL using �import a construct�.

Queries and discussions at: vigyan.forumotion.net